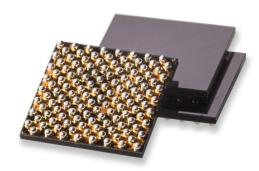

# eWLCSP

## **Encapsulated Wafer Level Chip Scale Package**

A compelling value proposition over standard WLCSP, this innovative encapsulated WLCSP technology offers the combined benefits of superior quality, lower cost structure and ease of conversion through drop-in replacement.

## **Highlights**

- Innovative FlexLine<sup>™</sup> manufacturing approach delivers compelling cost reductions over standard WLCSP

- Seamless conversion between fan-in and fan-out designs with the same basic package platform

- Unique WLP manufacturing approach independent of incoming silicon wafer diameter

## **Features**

#### Process

- Wafer agnostic process normalises wafer diameter to uniform processing size making incoming wafer size irrelevant

- All processing performed in wafer form before dicing

- eWLCSP structure identical to conventional WLCSP with exception of protective sidewall coating

- Final back grind thins the package to desired thickness

- Backside surface can be covered with mold compound, exposed with grind process or laminated with protective film

- Standard photolithography; Plated Cu RDL, Plated Cu UBM

- At least 30  $\mu m$  routing space at package edge compared to Si WLCSP

- Typical body thickness: ~300μm

- Same body sizes available as WLCSP (qualified up to 6x6mm); eWLCSP die size can be scaled beyond 6x6mm

- Ball pitch 0.50mm, 0.40mm, 0.35mm

- Fan-out panel/wafer level test before dicing

- Package singulation without touching Si after testing

#### Quality

- Polymer sidewall offers mechanical protection from die chipping, cracking and other handling issues

- >50% increase in die strength over traditional WLCSP structures

- Advanced dielectrics provide equal/better reliability and performance

- Benefits optimal for larger WLCSP die sizes

- Passes standard CLR, BLR, temperature cycle on board (TCoB) and drop test (equivalent to WLCSP)

#### Cost

- Drop-in replacement offers low risk, seamless conversion path from standard WLCSP

- Increased savings as panel sizes increase

- FlexLine process qualified at advanced silicon nodes down to 22/20nm

## **Robust Fan-in WLP Solution**

Customers with robust reliability requirements have the option of encapsulating the back and four sidewalls of a WLCSP die. This provides mechanical robustness and resistance to chipping, cracking and handling damage, enabling improved long term reliability over traditional bare die WLCSP. Encapsulation also provides significant structural protection for advanced node products where the die is very thin and dielectric layers are extremely fragile.

Utilizing our FlexLine<sup>™</sup> manufacturing approach, we offer an innovative encapsulated WLCSP technology called eWLCSP. With eWLCSP, the formation of a protective polymer coating on the back and four sides of the die surfaces is accomplished using the same high volume reconstitution and wafer level molding process that is used for our Fan-out wafer level technology known as embedded Wafer Level Ball Grid Array (eWLB).

eWLCSP provides a measurable increase in overall component break strength of more than 50% over traditional bare die WLCSP structures which are regularly exposed to potential cracking, chipping and handling issues that can occur before or during the SMT assembly process, especially in advanced node products where the die is very thin and dielectric layers are extremely fragile.

## Ease of Conversion, Lower Costs

An additional benefit of our FlexLine manufacturing process is the ease of conversion from a standard WLCSP to an eWLCSP design. Customers can seamlessly transition from a fan-in to fan-out design within the same basic package platform. A product currently using a conventional WLCSP process can be converted to eWLCSP without a silicon design change, regardless of the current silicon wafer diameter. 300mm devices transitioning to advanced silicon nodes with fragile dielectric layers will especially benefit from conversion to eWLCSP.

The FlexLine method can reduce WLCSP costs by 15-30% when using the optimum design requirements for WLCSP devices; e.g., 200mm incoming wafers can be reconstituted into 300mm or larger panel sizes, providing customers with the advantage of panel size scaling.

### **Process Highlights**

Passivation RL Line/Space Bump Pitch Visual Inspection 1 via size: 20μm (minimum) 8μm line/8μm space (minimum) 0.50mm, 0.4mm, 0.35mm, 0.3mm Automatic optical inspection with electronic wafer mapping

#### **Test Services**

Wafer level testing is an important process for yield enhancement and a final test requirement for eWLCSP. Our best-in-class test services include:

- Product Engineering support

- Probe capability

- Program generation/conversion

- High volume wafer sort

**Applications**

eWLCSP is a compelling solution for space constrained mobile devices and new applications such as wearable technology and automotive markets. Effective transition to eWLCSP is optimal for the following applications:

- 200mm WLCSP migration to FlexLine for PMIC and MCU applications

- 300mm WLCSP migration to eWLCSP for amplifiers, MCU, PMIC and RFIC applications

#### **Component Level Reliability Testing**

Moisture Sensitivity Level Temperature Cycling after Precon Unbiased HAST after Precon High Temperature Storage Temperature Humidity Bias Test Ball Shear Test MSL1, (260°C, 3x) -55°C/125°C, 1000 cycles 130°C/85% RH, 192 hrs 150°C, 1000 hrs 85°C/85%/5V, 1000 hrs Post reflow: T0, 5X and 10X; reflow: 260 +0/-5 °C

#### **Board Level Reliability Testing**

TC on Board (Condition B) Drop Test -40°C/125°C, 2 cycles/hr, 500 cycles Passed JEDEC drop test

#### **Thermal Performance**

- Thermal performance in the 20-40 C/W range for a 5mm x 5mm die without thermal enhancement

- Application specific thermal characterization available upon request

#### **Electrical Performance**

- Dependent on application design, and capable to beyond 10GHz

- Application specific electrical characterization available upon request

- Thick Cu for high current low inductance applications

## Cross Sections (Not to scale)

#### **FlexLine<sup>™</sup> Process Flow** Standard WLCSP eWLCSP with sidewall Si wafer backgrind Backgrind (opt) protective polymer casing Si wafer dicing Laser marking Lamination of foil onto carrier Chip placement 2 Reconstitution Pkg singulation Molding De-bonding of carrier 3 Redistribution Pkg pick & place Ball drop / reflow Ship in TnR Panel probe protective polymer casing Encapsulation offers sidewall protection The FlexLine process flow leverages the

The FlexLine process flow leverages the eWLB Fan-Out package process

**G**JCET

#### JCET Group Co., Ltd. www.jcetglobal.com

The JCET logo is a registered trademark of JCET Group Co., Ltd. Trademark registered in the People's Republic of China (registration number: 3000529). All other product names and other company names herein are for identification purposes only and may be the trademarks or registered trademarks of their respective owners. This brochure as well as datasheets herein are for presentation purposes only. JCET or its subsidiaries do not warrant or make any representation whatsoever, express, implied or statutory, as to the accuracy, adequacy, reliability, completeness or otherwise. Readers are advised to seek professional advice at all time and obtain independent verification of the information contained herein before making any decision. JCET reserves the right to change the information at any time and without notice. @Copyright 2019. JCET Group Co., Ltd. All rights reserved.