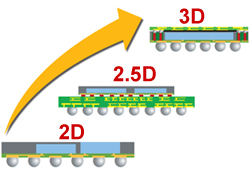

• 封装级集成

利用常规的焊线或倒装芯片工艺进行堆叠和互连,以构建传统的堆叠芯片和堆叠封装结构,包括:

堆叠芯片 (SD) 封装 ,通常在一个标准封装中使用焊线和倒装芯片连接,对裸片进行堆叠和互连。配置包括 FBGA-SD、FLGA-SD、PBGA-SD、QFP-SD 和 TSOP-SD。

层叠封装(PoP),通常对经过全面测试的存储器和逻辑封装进行堆叠,消除已知合格芯片 (KGD) 问题,并提供了组合 IC 技术方面的灵活度。倒装芯片 PoP 选项包括裸片 PoP、模塑激光 PoP 和裸片模塑激光 PoP 配置 (PoP-MLP-ED)。

封装内封装 (PiP) ,封装内封装 (PiP) 通常将已封装芯片和裸片堆叠到一个 JEDEC 标准 FBGA 中。经过预先测试的内部堆叠模块 (ISM) 接点栅格阵列 (LGA) 和 BGA 或已知/已探测合格芯片 (KGD),通过线焊进行堆叠和互连,然后模塑形成一个与常规FBGA封装相似的 CSP。